[This question paper contains 8 printed pages.]

Your Roll No.....

Sr. No. of Question Paper: 821

G

Unique Paper Code

: 2342572301

Name of the Paper

: Computer System Architecture

Name of the Course

: B.A. (Prog.) / Computer

Science 0

Semester

III

Duration: 3 Hours

Maximum Marks: 90

## Instructions for Candidates

- Write your Roll No. on the top immediately on receipt of this question paper.

- 2. Question No. 1 in Section-A is compulsory.

- Attempt any 4 questions from among questions 2 to 7 in Section-B.

- 4. Parts of a question must be answered together.

## Section-A

(a) Demonstrate the validity of the following identities by means of truth tables:

$$x + y.z = (x + y).(x + z)$$

(3)

- (b) Perform the following conversions:

- (i) (218.39)<sub>9</sub> to (\_)<sub>10</sub>

- (ii) (234)<sub>10</sub> to (\_)<sub>12</sub>

(3

- (c) How can you obtain a T flip-flop from JK flip. flop? Demonstrate using block diagram. (3)

- (d) The state of a 12-bit register is 190010110111.

What is its content if it represents:

- (i) The decimal digital BCD representation

- (ii) The decimal orgits in Binary coded octal representation

- (iii) The decimal digits in Binary coded hexadecimal representation (3)

- (e) Simplify the following Boolean expression to minimum number of literals using Boolean algebra:

$$(BC' + A'D)(AB' + CD')$$

(3)

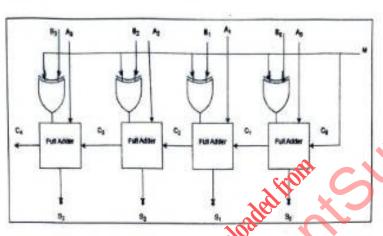

(f) The binary adder-subtractor circuit has the following values for the input-mode M and the data input A and B. Determine the values of the outputs S<sub>3</sub>, S<sub>2</sub>, S<sub>1</sub>, S<sub>0</sub>, and the carries generated i.e. C<sub>4</sub>, and C<sub>0</sub>.

$$M = 1$$

,  $A = 1011$ ,  $B = 0101$  (3)

- (g) Explain auto-decrement addressing mode with examples. (3)

- (h) Explain the "branch and save return address" operation with the help of a memory diagram.

(3)

- (i) Explain the importance of following condition bits:

- (i) FGO-flag

- (ii) E-flag

- (iii) I-flag (3)

- (j) Differentiate between half adder and full adder with the help of an example.

(3)

## Section-B

(a) Simplify the following Boolean expression in sumof-product (SOP) using K-map form and draw the logic diagram of the simplified expression.

Download all NOTES and PAPER

$$(A' + C)(A' + C')(A+B+C'D)$$

- (b) Describe what happens during an interrupt eyel with the help of memory diagram? Also Write th micro-instructions for the interrupt cycle. (5

- (c) A combinational circuit is specified by the following three Boolean functions:

$$F_1(A, B, C) = \Sigma(3, 5, 6)$$

$$F_2(A, B, C) = \Sigma(1, 4)$$

$$F_1(A, B, C) = \Sigma(3, 5, 6)$$

$F_2(A, B, C) = \Sigma(1, 4)$

$F_3(A, B, C) = \Sigma(2, 3)$

Construct the truth table for the above-mentioned circuit and implement the circuit with a decoder constructed with NAND gates. (6)

- 3. (a) Differentiate between combinational and sequential circuits and give two examples of each.

- (b) Perform the following arithmetic operations with binary numbers in signed 2's complement representation. Use 8-bit to accommodate each operand along with its sign. Identify in each case, if this operation results in overflow or not.

## Download all NOTES and PAPER

- (c) Write the micro-instructions for the execute sequence of following machine instructions:

- (i) Indirect mode STORE

- (ii) Direct mode ISZ

- (iii) Indirect mode BUN

(6)

- 4. (a) What is meant by bus request and bus growt with respect to direct memory access? (2)

- (b) (i) Perform subtraction on the given unsigned numbers using the 100 complement of the subtrahend;

6428 - 3409

- (ii) Construct the characteristic table for SR flipflop. (3+2)

- (c) The initial content of PC is 120. The content of memory at 120 is C1A0. The content of the memory at 1A0 is 0250. The content of memory at address 250 is 0134. Assuming the instruction has the format as mentioned below:

| I  | OPC |    | Address |   |

|----|-----|----|---------|---|

| 15 | 14  | 12 | 11      | 0 |

And 3-bit opcode for BUN is (100)<sub>2</sub> and BSA is (101)<sub>3</sub>.

P.T.O.

- (i) Specify the instruction that will be execut next and the addressing mode to be use

- (ii) Specify the micro-instruction to be execu sequentially for the fetch and execu sequence for the given instruction

- (iii) Show the contents in hexadecimal registers PC, AR, DR, IR and SC of the basic computer.

Give the answer in a table with 6-columns. Column 1 must contain the micro-instructions (response of part ii). Column 2-smust display the contents for each register and a row for each timing signal Show the content of registers after the positive transition of each clock-pulse.

- (a) Explain Index-register addressing mode with th help of an example. Also specify when/ where i it used.

- (b) Assuming the given data stored in 8-bit register Perform the following operations and represent the result obtained in hexadecimal:

$$A = (7C)_{16}, B = (65)_{16}$$

- (i) A (AND) B

- (ii) A (XOR) B

- (iii) 2's complement of B

- (iv) A B

- (v) Circular Shift right 2 times A. (5)

- (c) A computer uses a memory unit of 64M words of 36-bits each. A binary instruction code is stored in one word of the memory. The instruction has four parts:

- (i) An addressing mode field to specify one of the four-addressing modes,

- (ii) Operation code.

- (iii) A register code part to specify one of the 14 registers and an address part.

How many bits are there in addressing mode part, opcode part, register code part, and the address part? Draw the instruction format, clearly specifying the indexes and the number of bits for (6)each part.

- (a) Represent (-84)10 in 10 bits register using following representation:

- (i) Sign-magnitude representation

- (ii) 1's complement Representation

- (iii) 2's complement representation. (4)

- (b) How many address lines, data input lines and data output lines are present in a memory unit represented by 4096 × 16? How many 256 × 8 memory chips are needed to provide a memory capacity of 4096 × 16?

- (c) A two-word instruction is stored at location 500 with its address field at location 501. The address field has the content as 600 The content of memory word at address 600 is 650. A processor register R1 contains the number 300. Evaluate the effective address if the addressing mode of the instruction is

- (i) Immediate

- (ii) Direct

- (iii) Indirect

- (iv) Relative

- (v) Register-indirect

- (vi) Indexed with R1 as the index-register.

(6)

- (a) Draw the flowchart for the execute sequence of all memory reference instructions along with the control conditions.

- (b) Write short notes (any three):

- (i) Memory mapped I/O

- (ii) ISZ instruction

- (iii) Register reference Instructions

- (iv) Octal to decimal decoder (9)